Тактовані логічні схеми, крім інформаційних входів, мають один або кілька входів синхронізації. Тактові синхроімпульси дозволяють рознести у часі перехідні в різних каскадах логічних пристроїв, щоб уникнути помилкових спрацьовувань в моменти перемикання. Найпростішими прикладами можуть бути синхронний RS- і D-тригери. Досить часто використовують дві тактові послідовності синхроімпульсів з однаковою частотою, але зміщених половину періоду. У складних системах може використовуватися більше тактових послідовностей. Тактовані логічні пристрої працюють повільніше за асинхронні, складніше і споживають більше енергії живлення, але функціонують більш стійко.

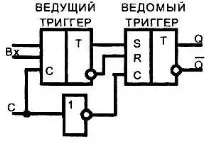

Тригери із двоступінчастим запам'ятовуванням інформації складаються з двох тригерів. Перший називається ведучим, другий - веденим т (рис. 1).

Обидва тригери – синхронні RS-тригери, але мають протилежні синхровходи. Ведучий тригер спрацьовує приС= 1, має прямий вхід, що синхронізує, а ведений приС= 0. Для цього синхроімпульс піддається інверсії.

На першому етапі, коли відбувається запис інформації до провідного тригера, ведений відключений і продовжує зберігати попередній стан. Коли синхроімпульс закінчується, провідний тригер перетворюється на режим зберігання і відбувається перезапис його стану ведений тригер. Таким чином відбувається поетапний запис інформації.

У двоступінчастому тригері усувається суперечність між процесами зберігання старої та прийому нової інформації. Це дає можливість побудови синхронних автоматів без небезпечних тимчасових станів, виключити передумови режиму генерацій. Дозволяє забезпечити високу надійність функціонування тригерів звнутрішніми ланцюгами зворотного зв'язку. У той самий час схеми цих тригерів складніші, ніж схеми тригерів з динамічним входом, а швидкодія нижче.

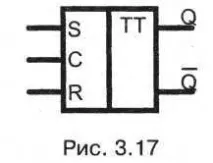

Часто двоступінчастий тригер називають MS-тригером від англійських слів «master» іslave— господар і раб. На важливих схемах двоступінчасті тригери позначаються здвоєної літерою(ТТ)рис. 2.

По структурі двоступінчастого тригера можна побудувати будь-які типи тригерів.

JK-тригери - це двоступінчасті універсальні синхронні тригери. Універсальність полягає в тому, що на їх основі можна зробити будь-який інший тип логічних тригерівRS,D, Т.

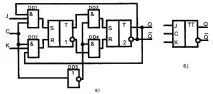

JKтригер є двоступінчастим тригером з додатковими зворотними зв'язками, що виключають появу заборонених комбінацій. Для цього його управління входами першого тригера побудовано на елементах 3І (DD1-DD2) і має два додаткові входи, на які подаються зворотні зв'язки. На рис. 3 наведена докладна схема та умовне зображенняJK-тригера.

При рівні логічного 0 на вході першийRS-тригер не реагує на сигнали входівJіК.При подачі на вхід С = 1 першийRS -тригер встановлюється в стан, що визначається сигналами наJіKвходах. При цьому зв'язок міжRS-тригерами обривається, тому що елементи ІDD3-DD4встановлюються в нульовий стан. Подача знову сигналу С = 0 на синхровхідJK-тригера призводить до відключення першогоRS-тригера від вхідних сигналів через елементиDD1,DD2.Однак, приС= 0 через інверторDD5на входи елементівDD3,DD4надходить логічна одиниця та стан першого>RS-тригера перезаписується вдругий.

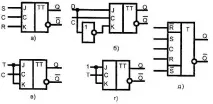

На основіJK-тригера може бути побудований будь-який інший тригер (рис.4). На рис.4, а - синхроннийRS-тригер, на рис.4, б -D-тригер, на рис.4, - синхроннийТ-тригер, на рис.4, г - асинхроннийT-тригер.

JK-тригер, як і інші типи тригерів, може додатково мати входи початкової установки (рис.4, д), які є інверсними по відношенню до входівJ.K.

JK-тригери - це складніші тригери, містять більшу кількість елементів, тому споживана потужністьРпотвиявляється великою. Заходи, що вживаються для зменшення споживаної потужності, нерідко призводять до погіршення частотних властивостей.JK-тригер внаслідок своєї універсальності та відсутності заборонених комбінацій знаходить широке застосування в цифровій техніці.